|

||

Accueil > Hackathon

HPC Hackathon

Industrial code optimization

We aim with this hackathon to bring together Master II-level HPC students in a virtual competition around computational codes provided mostly by Electricité De France - EDF (Saturn and Telemac code) and CGG (seismic core). Other industrial partners might complete this first list.

This competition will rely on Amazon Web Services - AWS instances based on Arm technologies. Indeed, the target architectures (AWS Graviton 2 and 3 processors) offer certain approaches (software ecosystem, design) that motivate a specific effort compared to traditional Intel or AMD type architectures. Typically, on the Graviton 3 processor, we can mention the use of SIMD units (Scalable Vector Extension/SVE compared to AVX2 or AVX-512 on x86 architectures) or the availability of 8 DDR5 memory channels. .

This hackathon is structured around computational codes, software environments and hardware solutions that have already been tested by industry. The compilation recipes and optimization phases have been validated before the event. The students will therefore be in a framework close to a guided practical session with the opportunity to increase their understanding of industrial issues around high-performance simulation. No specific contributions from students in terms of porting or optimization are expected (these codes are largely proven in a production context and on multiple hardware architectures). The participants will nevertheless be credited by the industrial partners (the codes have an open status) in case of significant advances..

Students are encouraged to take an iterative approach to porting and optimizing these industrial codes/kernels. The latter are of different nature/complexity and will allow the deployment of the classical phases of taking control of a scientific application. The evaluation of the teams (4 students maximum per team) will be based on the following points:

- Porting: it will be a question of validating the application on Arm architectures (Graviton2/Graviton3) by focusing on the test case provided by the industrial partner. The validation will be done by comparing the result files and/or by comparing the results on different platforms (x86/Arm).

- Profiling: Students will be asked to use classical application profiling tools to identify performance locks... this will include identifying the hotspots of these applications (compiler report, dynamic code analysis...)

- Advanced optimization: During this phase, the students will be able to make some modifications to the codes in order to improve the performances. For small applications (e.g., CGG code, this may involve adding OpenMP directives or modifying the organization of loops ...). In the case of complex code, participants can focus on the impact of the different compilation chains and work on extracting some kernels (mini-apps). The latter could then be the subject of specific efforts.

- Arm, Nvidia and GNU compilers will be available during the hackathon. Students will also have access to various code profiling tools (e.g., Arm Allinea Forge).

- The synthesis of the obtained results (compilation recipes, validation procedure, optimization, loops extraction ...) will be made available on a Git repository in order to facilitate the evaluation and the reproducibility.

CGG

- Focus: numerical validation (x86 Intel/AMD comparison), evaluation of different compilers (Arm, Nvidia, GNU), Vectorization

EDF

- Focus: porting and numerical validation (intel/AMD comparison), evaluation of different compilers, possibly extraction of kernels (hotspots) for advanced analysis.

- Focus: porting and numerical validation (intel/AMD comparison), evaluation of different compilers, possibly extraction of kernels (hotspots) for advanced analysis

| Code Saturne | Code Stencil | Système Telemac | ||

|

|

|

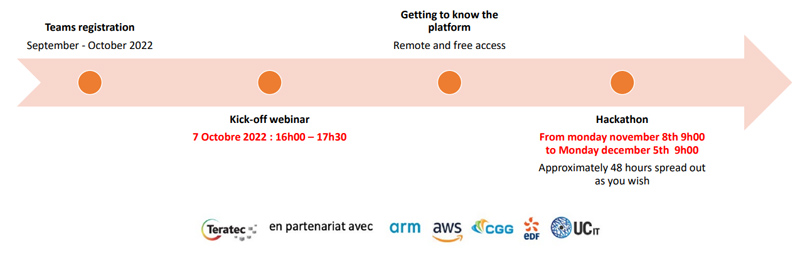

• Download the Hackathon presentation document

• Download the slides presented during the kick-off Hackathon webinar on October 7, 2022

• Download the press release (in french) announcing the winning teams

• View the video of the october 7th webinar:

| Contacts : | ||

| TERATEC : | Emmanuelle Vergnaud | emmanuelle.vergnaud@teratec.fr |

| ARM : | Conrad Hillairet | conrad.hillairet@arm.com |

| AWS : | Gilles Tourpe | gtourpe@amazon.com |