|

||

Hackathon HPC

Optimisation de codes industriels

Principe

Avec ce hackathon, nous visons à rassembler les étudiants HPC de niveau M2 dans une compétition virtuelle autour des codes de calcul fournis notamment par EDF et la CGG.

Cette compétition s'appuiera sur les instances AWS basées sur les technologies Arm. En effet, les architectures cibles (processeur AWS Graviton 2 et 3) proposent certaines approches (écosystème logiciel, design) motivant un effort spécifique par rapport aux architectures classiques de type Intel ou AMD. Typiquement, sur le processeur Graviton3, on peut citer l'exploitation des unités SIMD (Scalable Vector Extension/SVE par rapport à l'AVX2 ou l'AVX-512 sur architectures x86) ou encore la disponibilité de 8 canaux mémoire de type DDR5.

Ce hackathon est structuré autour de codes de calcul, d'environnements logiciels et de solutions matérielles déjà éprouvés par les industriels. Les recettes de compilation, les phases d'optimisation ont été validées en amont de cet événement. Les étudiants seront donc dans un cadre proche d'une session de travaux pratiques guidés avec l'opportunité d'accroitre leur compréhension des enjeux industriels autour de la simulation haute performance. Il n'est donc pas attendu de contributions spécifiques venant des étudiants en termes de portage ou d'optimisation (ces codes sont largement éprouvés dans un contexte de production et sur de multiples architectures matérielles). Les participants seront néanmoins crédités par les partenaires industriels (les codes ont un statut ouvert) en cas d'avancées significatives.

Modalités

Les étudiants sont encouragés à adopter une approche itérative pour le portage et l’optimisation de ces codes/noyaux industriels. Ces derniers sont de nature/complexité différentes et permettront de déployer les phases classiques de prise en main d’une application scientifique. L’évaluation des équipes (4 étudiants maximum par équipe) se fera notamment autour des points suivants

- Portage : il s'agira de valider l'application sur architectures Arm (Graviton2/Graviton3) en se focalisant sur le cas test fourni par le partenaire industriel. La validation s'effectuera par le biais d'une comparaison des fichiers résultats et/ou en comparant les résultats sur différentes plateformes (x86/Arm).

- Profiling : Il est demandé aux étudiants d'utiliser les outils classiques de profilage des applications permettant d'identifier les verrous en termes de performance… il s'agira notamment d'identifier les hotspots de ces applications (rapport du compilateur, analyse dynamique du code…)

- Optimisation avancée : Durant cette phase, les étudiants pourront apporter certaines modifications aux codes afin d'améliorer les performances. Pour les applications de taille modeste (e.g. code CGG, il pourra s'agir de rajouter des directives OpenMP ou de modifier l'organisation des boucles …). Dans le cas des codes complexes, les participants pourront se concentrer sur l'impact des différentes chaines de compilation et travailler à l'extraction de certains noyaux (mini-apps). Ces dernières pourraient par la suite faire l'objet d'efforts spécifiques.

— Les compilateurs Arm, Nvidia et GNU seront notamment disponibles durant ce hackathon. Les étudiants auront également accès à différents outils de profiling de codes.

— La synthèse des résultats obtenus (recettes de compilation, procédure de validation, optimisation, extraction de boucles …) sera mise à disposition sur un dépôt de type Git afin de faciliter l’évaluation et la reproductibilité.

Codes proposés / Noyaux identifiés (Septembre 2023)

CGG

Fonction Zêta de Riemann : www.cgg.com

- Focus : optimisation d'un code numérique, depuis l'algorithme haut niveau jusqu'aux optimisations bas niveau "vectorisation,..". Parallélisation du code. Ceci reflète des cas réels où l'on prend une application "non optimisée" et "non parallélisée" d'un expert scientifique qui souhaite accélérer fortement son code sur une architecture spécifique. Forte capacité de transformations tant que le résultat final est correct.

EDF

Code Telemac : http://www.opentelemac.org

- Focus : portage et validation numérique (comparaison intel/AMD), évaluation de différents compilateurs, éventuellement extraction de noyaux (hotspots) pour analyse avancée.

Format

Planning :

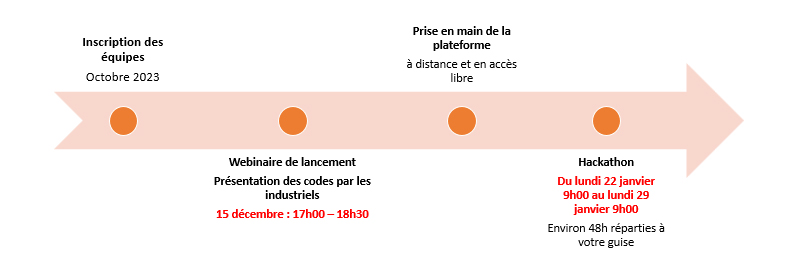

• Inscription des équipes : jusqu'au 10 novembre 2023

• Webinar de présentation : vendredi 15 décembre 17h00 -18h30

• Présentation du hackathon, des différents partenaires et de l'intérêt industriel des codes traités + questions / réponses

• Webinar enregistré et disponible en ligne toute l'année.

• Session dédiée à la formation aux outils disponible en ligne début janvier

• Hackathon du lundi 22 janvier 2024 9h00 au lundi 29 janvier 9h00

• Travail estimé à 48h laissé au choix de l'institution dans le cadre de la semaine

• Equipe de 4 étudiants

• Support Arm/AWS/UCIT du lundi 22 janvier 2024 9h00 au vendredi 26 janvier 19h00

• Remise des prix et retour d'expériences des élèves le 30 mai 2024 lors du Forum TERATEC.

Prix

La compétition donnera lieu à un classement. La première équipe recevra 4 MacBook Air offerts par les sociétés Arm et CGG La deuxième équipe des lots offerts par les sociétés UCIT et EDF

• Télécharger le document de présentation du Hackathon

• Télécharger le Flyer de présentation

• Télécharger les slides présentés lors du webinaire de lancement du 15 décembre 2023

• Visionner le webinaire de lancement du 15 décembre :

Teratec Hackaton HPC 2024 : LA REMISE DES PRIX!

Félicitations aux 50 étudiants (13 équipes !) qui se sont lancés dans des simulations sur des environnements Arm HPC dans le cloud Amazon Web Services (AWS) et aussi à leurs professeurs !

Voici le podium :

- "Prix spécial du jury" : Team « La Team » de l'URCA !

- 3ème place : Team « Euteam4Hpc » de FAU

- 2ème place : Team « Chips » 24 de l'UVSQ

- 1er prix : Team « Unimplemented » de l'UVSQ

La cérémonie de remise des prix s'est déroulée lors du Forum Teratec 2024, à Vincennes (Parc Floral de Paris), le 30 mai 2024.

Les prix comprenaient 4 MacBook Air pour les gagnants et d'autres belles récompenses pour les autres équipes !

| Contacts : | ||

| TERATEC : | Emmanuelle Vergnaud | emmanuelle.vergnaud@teratec.fr |

| Andréa Ralamboson | andrea.ralamboson@teratec.fr | |

| ARM : | Conrad Hillairet | conrad.hillairet@arm.com |

| AWS : | Gilles Tourpe | gtourpe@amazon.com |

| UCit : | Benjamin Depardon | benjamin.depardon@ucit.fr |