## Scaling the QCCD Architecture for Trapped-Ion Quantum Computers

Presented by Alistair Milne

13th November 2024

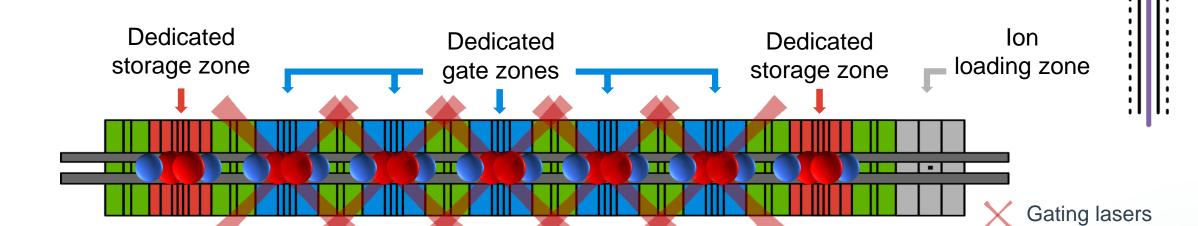

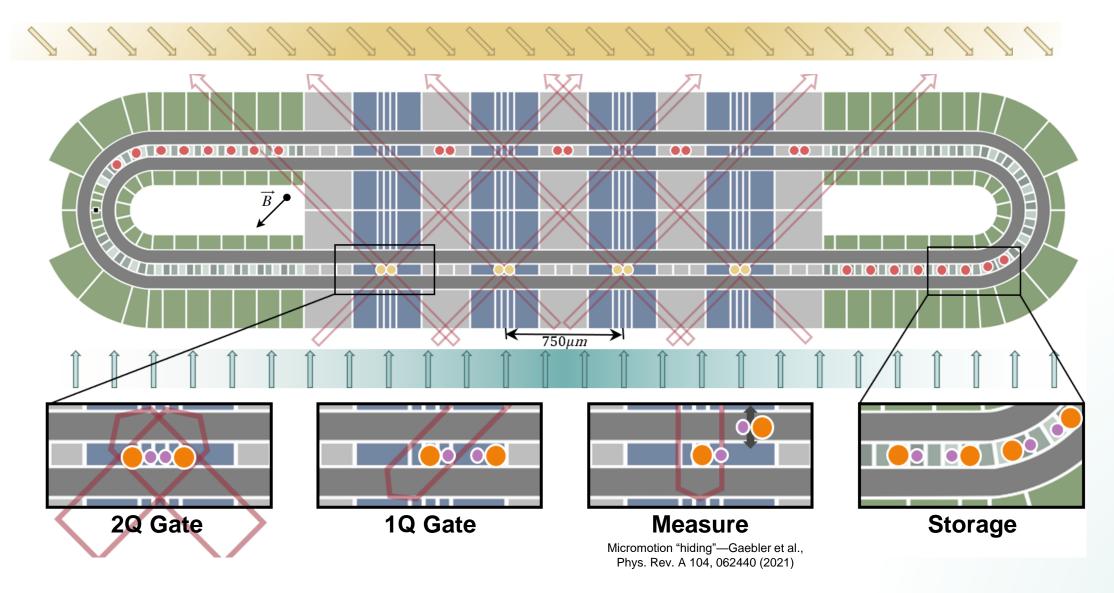

## **QCCD Trapped-Ion Architecture**

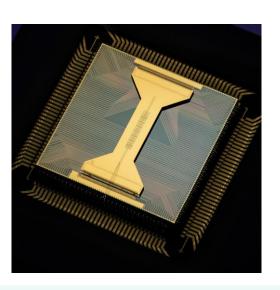

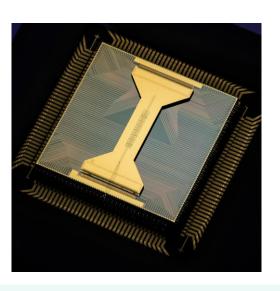

#### **H1 Generation Ion Trap Architecture**

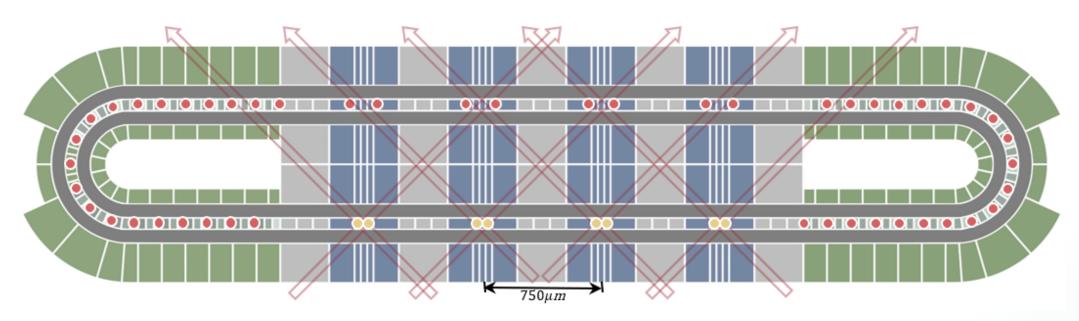

Quantum bits (qubits) are stored in the electronic states of identical Yb<sup>+</sup> ions.

QCCD architecture enables using gate zones

Single qubit gates, two qubit gates and state detection all performed using lasers Cooling ions provide mid-circuit cooling, maintaining circuit fidelity throughout circuit.

<sup>138</sup>Ba+

Cooling ion

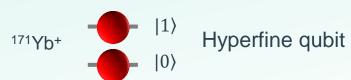

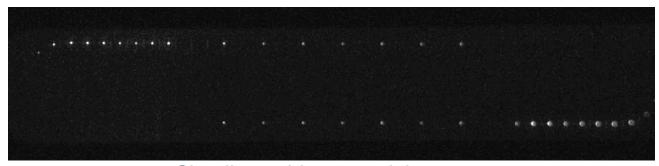

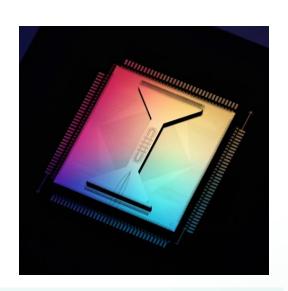

## System Model H2: 56 qubit trapped-ion processor

Shuttling qubits around the trap

#### **Transport primitives**

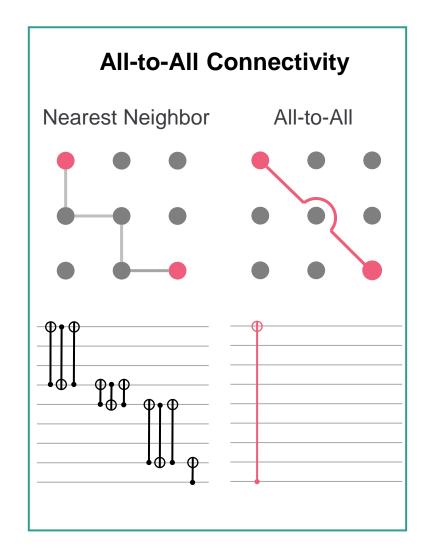

Enable arbitrary sorting of ions and allto-all connectivity

## QCCD architecture: differentiating features

- 56 qubits, 1540 qubit pairings

- 4 gate zone calibrations

- Not 1540 qubit pair calibrations

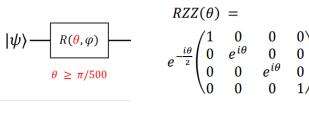

## Arbitrary Angle 1-qubit and 2-qubit gates

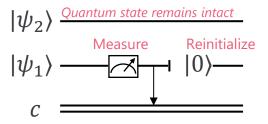

#### **Qubit Measurement and Reuse**

Measurement and reuse

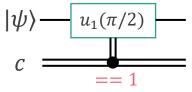

Conditional logic

If

$$c==1$$

, perform gate

If  $c==0$ , do not

## Quantinuum's commercial systems

Hardware specifications and benchmarking data available

at:

https://github.com/CQCL/quantinuum -hardware-specifications/

| Qubits                       | 20 fully-connected                               | 56 fully-connected           |  |

|------------------------------|--------------------------------------------------|------------------------------|--|

| 1Q Gate Error                | 2.1(3)×10 <sup>-5</sup>                          | 2.9(4)×10 <sup>-5</sup>      |  |

| 2Q Gate Error                | $8.8(3) \times 10^{-4}$ 1.28(8)×10 <sup>-3</sup> |                              |  |

| SPAM Error                   | 2.5(1)×10 <sup>-3</sup>                          | 1.5(1)×10 <sup>-3</sup>      |  |

| Measurement Crosstalk Error  | 1.5(1)×10 <sup>-5</sup>                          | 7.4(8)×10 <sup>-6</sup>      |  |

| Memory Error                 | 2.1(2)×10 <sup>-4</sup>                          | 5.0(5)×10 <sup>-4</sup>      |  |

| Quantum Volume               | 1 048 576 (2 <sup>20</sup> )                     | 2 097 152 (2 <sup>21</sup> ) |  |

| Mirror Benchmarking (Qubits) | 1.4(2)×10 <sup>-3</sup> (20)                     | 2.5(1)×10 <sup>-3</sup> (56) |  |

| GHZ State Fidelity (Qubits)  | 81.6(8)% (20)                                    | 61.6(8)% (56)                |  |

| Depth-1 Circuit Time         | 21 ms                                            | 70 ms                        |  |

## Quantinuum's commercial systems

Hardware specifications and benchmarking data available

at:

https://github.com/CQCL/quantinuum -hardware-specifications/

| Qubits                       | 20 fully-connected           | 56 fully-connected           |

|------------------------------|------------------------------|------------------------------|

| 1Q Gate Error                | 2.1(3)×10 <sup>-5</sup>      | 2.9(4)×10⁻⁵                  |

| 2Q Gate Error                | 8.8(3)×10 <sup>-4</sup>      | 1.28(8)×10 <sup>-3</sup>     |

| SPAM Error                   | 2.5(1)×10 <sup>-3</sup>      | 1.5(1)×10 <sup>-3</sup>      |

| Measurement Crosstalk Error  | 1.5(1)×10 <sup>-5</sup>      | 7.4(8)×10 <sup>-6</sup>      |

| Memory Error                 | 2.1(2)×10 <sup>-4</sup>      | 5.0(5)×10 <sup>-4</sup>      |

| Quantum Volume               | 1 048 576 (2 <sup>20</sup> ) | 2 097 152 (2 <sup>21</sup> ) |

| Mirror Benchmarking (Qubits) | 1.4(2)×10 <sup>-3</sup> (20) | 2.5(1)×10 <sup>-3</sup> (56) |

| GHZ State Fidelity (Qubits)  | 81.6(8)% (20)                | 61.6(8)% (56)                |

| Depth-1 Circuit Time         | 21 ms                        | 70 ms                        |

## Quantinuum's commercial systems

Hardware specifications and benchmarking data available

at:

https://github.com/CQCL/quantinuum -hardware-specifications/

| Qubits                       | 20 fully-connected           | 56 fully-connected           |

|------------------------------|------------------------------|------------------------------|

| 1Q Gate Error                | 2.1(3)×10 <sup>-5</sup>      | 2.9(4)×10 <sup>-5</sup>      |

| 2Q Gate Error                | 8.8(3)×10 <sup>-4</sup>      | 1.28(8)×10 <sup>-3</sup>     |

| SPAM Error                   | 2.5(1)×10 <sup>-3</sup>      | 1.5(1)×10 <sup>-3</sup>      |

| Measurement Crosstalk Error  | 1.5(1)×10 <sup>-5</sup>      | 7.4(8)×10 <sup>-6</sup>      |

| Memory Error                 | 2.1(2)×10 <sup>-4</sup>      | 5.0(5)×10 <sup>-4</sup>      |

| Quantum Volume               | 1 048 576 (220)              | 2 097 152 (2 <sup>21</sup> ) |

| Mirror Benchmarking (Qubits) | 1.4(2)×10 <sup>-3</sup> (20) | 2.5(1)×10 <sup>-3</sup> (56) |

| GHZ State Fidelity (Qubits)  | 81.6(8)% (20)                | 61.6(8)% (56)                |

| Depth-1 Circuit Time         | 21 ms                        | 70 ms                        |

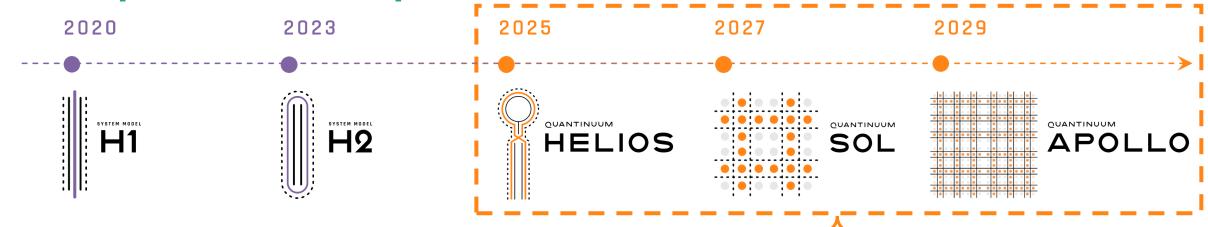

### **Development roadmap**

|                                    | 2020                 | 2023                 | 2025                   | 2027                   | 2029                                            |

|------------------------------------|----------------------|----------------------|------------------------|------------------------|-------------------------------------------------|

| SYSTEMS:                           | SYSTEM MODEL  H 1    | H2                   | HELIOS                 | SOL                    | APOLLO                                          |

| PHYSICAL<br>QUBITS:                | 20                   | 56                   | 96                     | 192                    | 1000's                                          |

| PHYSICAL<br>2-QUBIT<br>GATE ERROR: | 1 × 10 <sup>-3</sup> | 1 × 10 <sup>-3</sup> | < 5 × 10 <sup>-4</sup> | < 2 × 10 <sup>-4</sup> | 1 × 10 <sup>-4</sup>                            |

| LOGICAL<br>QUBITS:                 |                      | > 12                 | ~ 50                   | ~ 100                  | 100's                                           |

| LOGICAL<br>ERROR<br>RATES:         |                      | 1 × 10 <sup>-3</sup> | < 10 <sup>-4</sup>     | ~ 10 <sup>-5</sup>     | 1 × 10 <sup>-5</sup> to 1 × 10 <sup>-10</sup> * |

### **Development roadmap**

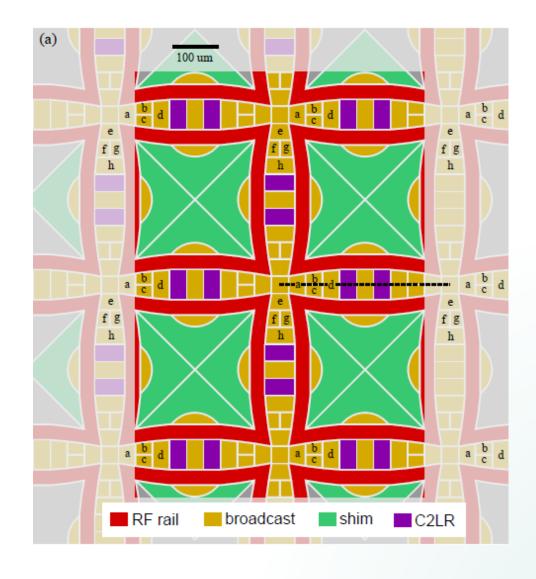

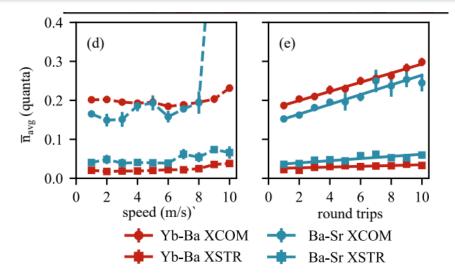

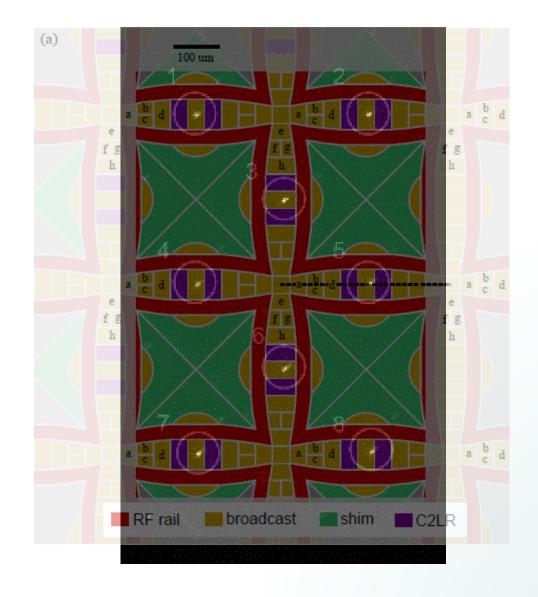

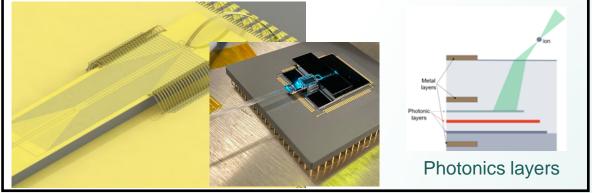

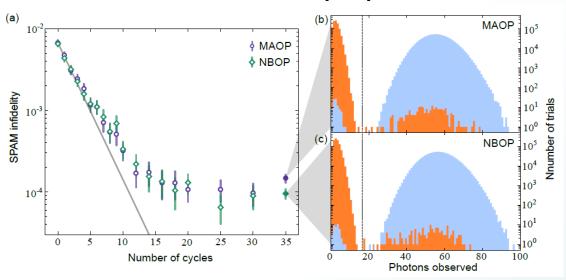

## 2D grid with scalable electronics

R. Delaney et al., Multispecies Ion Transport in a Grid Based Surface-Electrode Trap, arXiv:2403.00756 (2024)

Integrated photonics for beam delivery

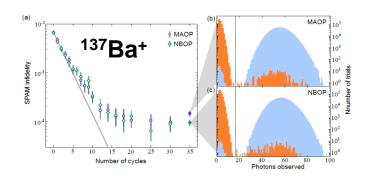

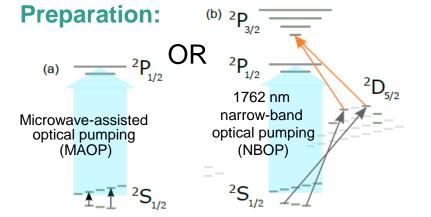

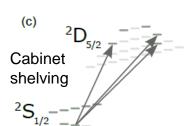

## New qubit with high SPAM fidelity

F. A. An et al., Phys. Rev. Lett. 129, 130501 (2022)

**Universal, Fault-Tolerant Quantum Computing**

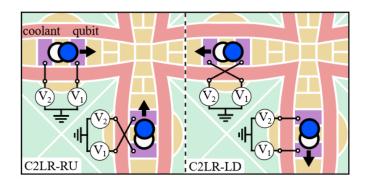

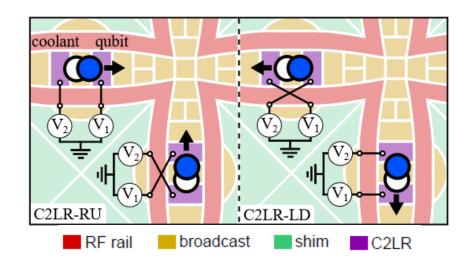

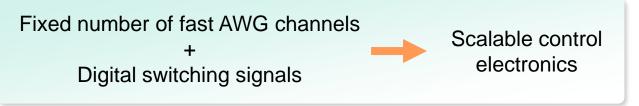

## Scalable wiring for 2D grid

- 2D grid traps enable fast all-to-all connectivity

- Without a mitigation strategy, wiring scales linearly

- C2LR scheme: broadcast RF signals + 1 digital signal per zone

Fixed number of fast AWG channels

+

Digital switching signals

Scalable control electronics

## Scalable wiring for 2D grid

- 2D grid traps enable fast all-to-all connectivity

- Without a mitigation strategy, wiring scales linearly

- C2LR scheme: broadcast RF signals + 1 digital signal per zone

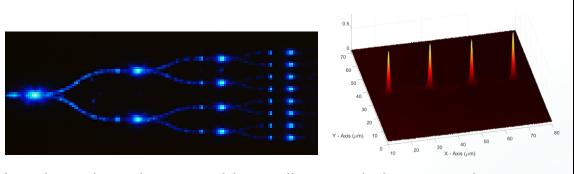

## **Photonics integration**

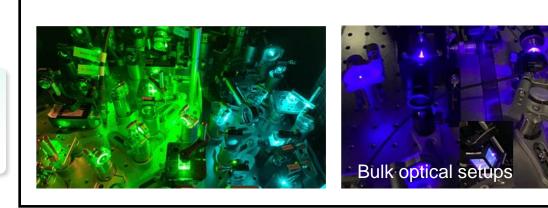

Free-space bulk + fiber optics: large physical footprint, complex alignment

Photonics for beam delivery and conditioning: decrease physical footprint and reduce alignment complexity

Integrated photonics in trap structure, metamaterials for in-vacuum beam shaping and control

Low-loss photonic waveguides, splitters, polarizers, couplers

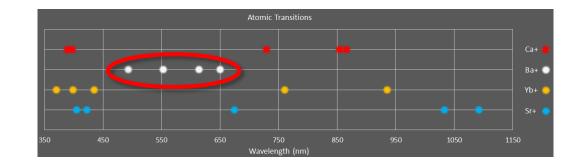

## <sup>137</sup>Ba+: qubit for scale

- Visible laser wavelengths more compatible with integrated photonics. No high-power UV required.

- Low SPAM error

#### **State**

#### **Detection:**

#### SPAM error: 9.6(1.4)×10<sup>-5</sup>

An, Fangzhao Alex, et al. High fidelity state preparation and measurement of ion hyperfine qubits with I > 1/2, Phys. Rev. Lett. 129, 130501 (2022).

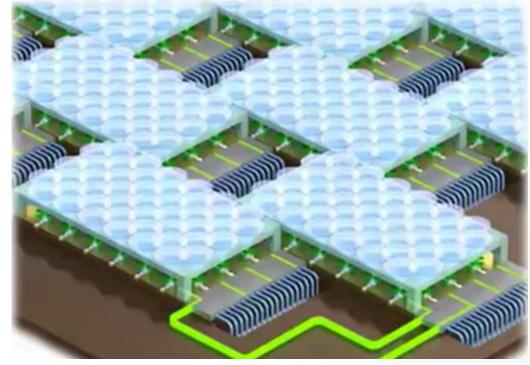

## Modular architectures with trapped ions

- Near term: increase qubit density on single chip (50,000 qubits on a single square-inch dye)

- Long term: trap tiling to scale to millions of qubits (30 cm x 30 cm area)

- Qubits distributed between modules via ion transport

- Beams delivered via integrated photonics

Tiled trap modules

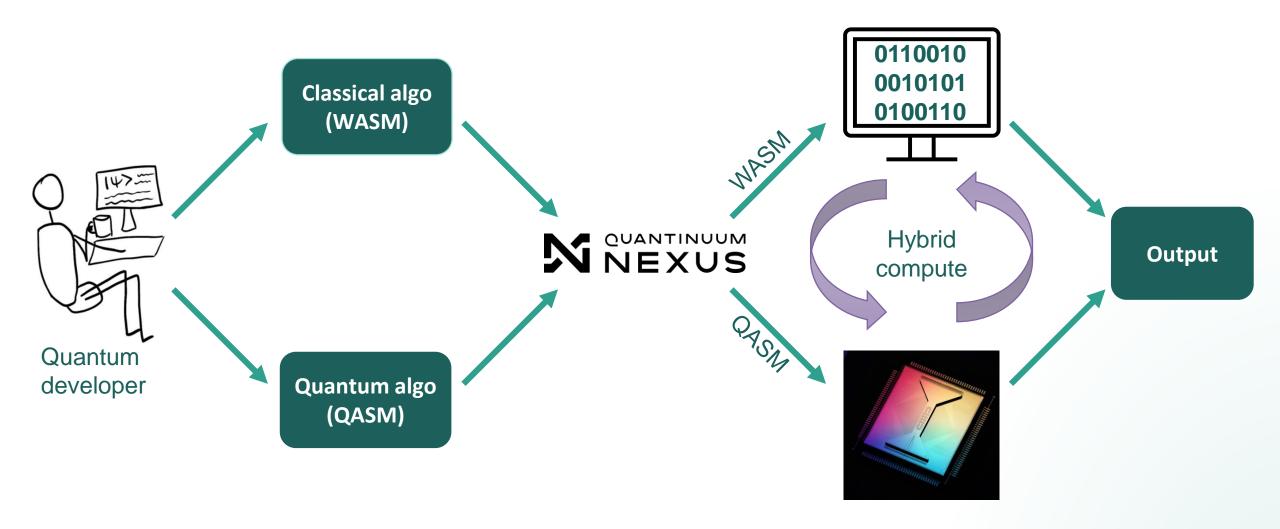

## **Quantinuum's Quantum Computing Infrastructure**

#### INQUANTO

Next generation of molecular and materials discovery

#### **Algorithm Libraries**

Quantum Machine Learning

Quantum Monte Carlo Integration

Quantum Natural Language Processing

#### Third party software

Enables other partners to leverage the power of quantum

Quantum workflow orchestration platform

TKET

Multi-platform quantum SDK | Open-source

**Quantum Error Correction:** Quantinuum and partners

#### QUANTINUUM SYSTEMS

The world's highest-performing quantum hardware

Other quantum computers

# Thank you

## System Model H2: 56 qubit trapped-ion processor

## **Fault-tolerant Quantum Computing Infrastructure**

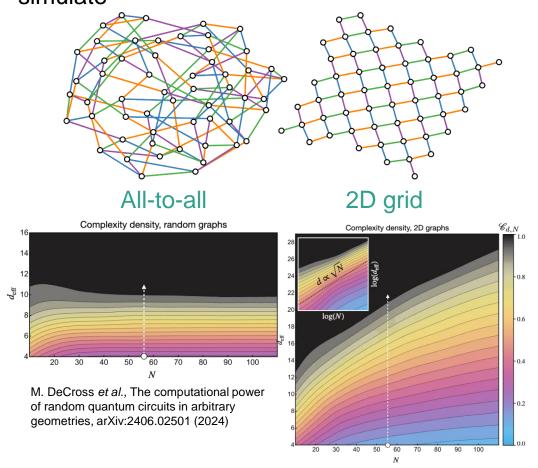

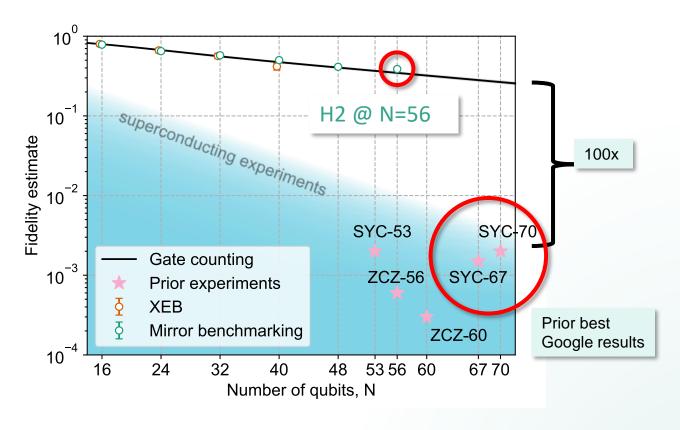

## Exceeding classical computing: random circuit sampling

All-to-all connectivity: much harder to classically simulate

Executed with 100x better fidelity than previous demonstrations

F. Arute, et al., Nature **574**, 505 (2019). Q. Zhu, et al., Science Bulletin **67**, 240 (2022) A. Morvan, et al., arXiv 2304.11119 (2023). M. DeCross et al., arXiv 2406.02501

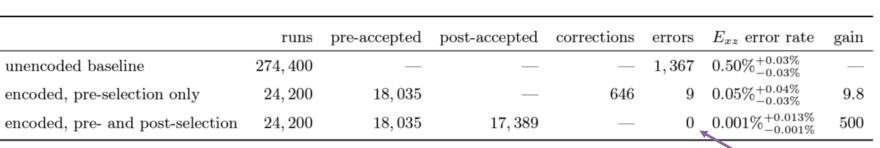

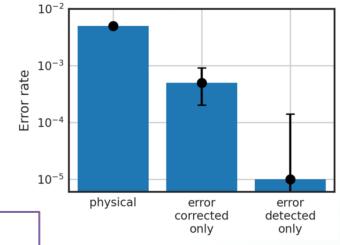

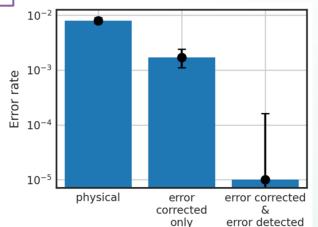

# Demonstration of logical qubits and repeated error correction with better-than-physical error rates

>10<sup>4</sup> trials with 0 errors

Bell state preparation: [[7,1,3]] Steane code

#### Bell state preparation: [[12,2,4]] Carbon code

|                                  | runs   | pre-accepted | post-accepted | corrections | errors | $I_{xz}$ error rate             | gain |

|----------------------------------|--------|--------------|---------------|-------------|--------|---------------------------------|------|

| unencoded baseline               | 16,000 | 16,000       | _             | _           | 125    | $0.8^{+0.1}_{-0.1}\%$           | _    |

| encoded, pre-selection only      | 22,000 | 15,483       | _             | 928         | 26     | $0.17^{+0.07}_{-0.06}\%$        | 4.7  |

| encoded, pre- and post-selection | 22,000 | 15,483       | 15,409        | 854         | 0      | $0.001\%^{+0.015\%}_{-0.001\%}$ | 800  |

M. P. da Silva *et al.,* arXiv 2404.02280

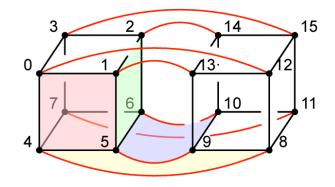

# Demonstration of quantum computation and error correction with a tesseract code

FIG. 1. The [[16, 6, 4]] color code on the 4D hypercube, or tesseract. Each of the 16 vertices is a qubit. Cubes are X and Z stabilizers, and squares are logical operators, e.g., 0145.

More complex structure (compared to 2D surface code)

Benefits from all-to-all connectivity

| Experiment                                                                                          | Qubits | Baseline error rate | Encoded error rate       | Gain       |

|-----------------------------------------------------------------------------------------------------|--------|---------------------|--------------------------|------------|

| Path-4                                                                                              | 4      | 1.5(2)%             | $0.10^{+0.11}_{-0.06}\%$ | $15\times$ |

| Cube-8                                                                                              | 8      | 2.3(3)%             | $0.2^{+0.2}_{-0.1}\%$    | $11\times$ |

| $ {}^{\scriptscriptstyle{0^{12}}\rangle} +  {}^{\scriptscriptstyle{1^{12}}\rangle} \ Cat\text{-}12$ | 12     | 2.4(3)%             | $0.11^{+0.16}_{-0.08}\%$ | $22\times$ |

| Error correction 5>                                                                                 | , 4    | 2.7(4)%             | $0.11^{+0.21}_{-0.09}\%$ | $24\times$ |

| Entor correction 57                                                                                 | 8      | 5.6(6)%             | $0.7^{+0.7}_{-0.4}\%$    | $8 \times$ |

12-logical-qubit GHZ state prep with ~99.9% fidelity (22x better than 12-physical-qubit GHZ state prep)

B. W. Reichardt et al., arXiv 2409.04628