|

||

Accueil > FORUM TERATEC > Programme > Atelier 5

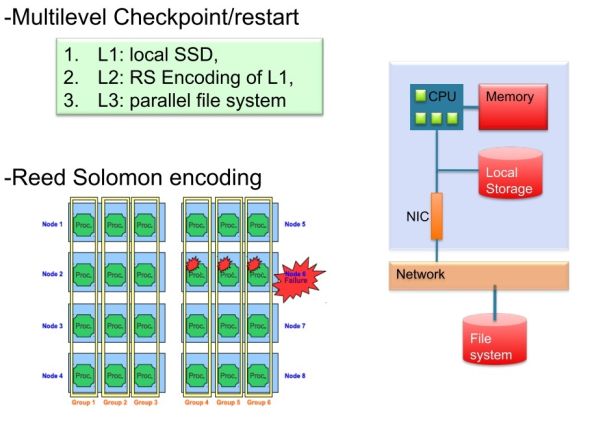

Advanced Multi Fault Tolerance in parallel applications: Multi level storage with FTI middleware Eric BOYER Abstract : Fault tolerance is a key concern for future HPC systems. Checkpointing delay on a global file system increases dramatically as scaling grows and MTTI reduces as expected with the increasing of hardware components expected in future Exascale systems. The approach used by AMFT relies on the usage of different storage level, using asynchronous processes, to unleash scalability. The FTI library is available at application level to implement advanced checkpointing features. This project has started at INRIA in 2010 with TiTech. Then a contribution from CEA, CINES and GENCI was initiated through a PRACE prototype. The FTI library was enriched by new features and assessed at CEA-TGCC and at CINES. . « Advanced Multi Fault Tolerance » dans les applications parallèles: Stockage multi- niveaux avec l’intergiciel FTI Résumé : La tolérance de panne est une préoccupation majeure pour les prochaines de calcul. Le temps des points de reprise sur un système de fichiers global augmente considérablement lors du passage à l’échelle et de la réduction du MTTI qui accompagnera l’accroissement de composants des futurs, systèmes Exaflopiques. L'approche utilisée par AMFT repose sur l’utilisation de plusieurs niveaux de stockage en introduisant des processus asynchrones, déverrouillant le passage à l’échelle. La bibliothèque FTI est disponible au niveau de l'application pour mettre en œuvre les fonctions avancées de points de reprise. Ce projet a commencé à l'INRIA en 2010 avec TiTech. Ensuite, une contribution du CEA, GENCI et le CINES a été lancé par un prototype de PRACE. La bibliothèque de FTI a été enrichie par de nouvelles fonctionnalités et évaluée au CEA-TGCC et au CINES.

|

![]() La participation à cet atelier est gratuite sous réserve des places disponibles

La participation à cet atelier est gratuite sous réserve des places disponibles

![]() L'enregistrement en ligne est obligatoire pour y assister. Cliquer ICI pour vous inscrire.

L'enregistrement en ligne est obligatoire pour y assister. Cliquer ICI pour vous inscrire.